Assertion-Based Verification _ 针对assertion based验证的一些“建议”和“不建议”

Di: Stella

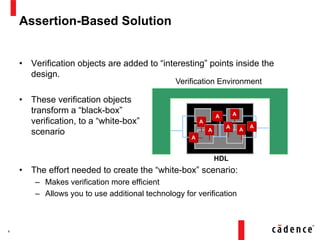

Assertion Based Verification (ABV) has become a main stream verification methodology. Assertions serve as white-box specification by defining temporal relationship among internal design signals, and ABV is the key to improve observability when verifying complex SoC designs. This tutorial focuses on several aspects of ABV for the benefit of hardware design and Overall Recommendations Assertion-based FV: important part of design Plan for it from the beginning Major principles #1: Highly Usable Libraries #2: Make Assertions Happen #3: Lay Groundwork For Formal #4: Make Formal Verification Work

针对assertion based验证的一些“建议”和“不建议”

Abstract Debugging, on average, has grown to consume more than 60% of today’s ASIC and SoC verification effort. Clearly, this is a topic the industry must address, and some organizations have done just that. Those that have adopted an assertion-based verification (ABV) methodology have seen significant reduction in simulation debugging time (as much as 50% [1]) due to improved However, with the recent advancement of transformer models, the Large Language Models (LLMs) assisted assertion generation for design verification is gaining interest in recent times. Motivated by this, we proposed a novel LLM-based framework, LAAG-RV, to generate SVA from the natural language specifications of the design.

In this chapter, the authors introduce a new approach to addressing the functional verification challenge, known as assertion-based verification, which provides a unified methodology for unambiguously specifying design intent across multiple verification processes using assertions. Assertion-Based Verification The process of creating assertions forces the engineer to think. . . and in this incredible world of automation, there is no substitute for thinking.

System Verilog assertions always help to speed up the verification process and it’s very powerful and widely used in the ASIC verification. Identifying the right set of checkers in the verification plan and implementing them using effective SV assertions helps to quickly catch the design bugs and ultimately helps in high-quality design. With the ever-increasing Assertion-based verification is a promising method that uses predefined rules, known as assertions, to check the functionality of hardware designs. The manual assertion definition is time-consuming and requires expert knowledge. Automatic assertion mining is gaining acceptance as a trustworthy method for assertion definition. Some automatic assertion miners extract assertions

Welcome to the Assertion Based Verification – SVA course – your comprehensive guide to mastering SystemVerilog Assertions (SVA). From understanding the basics to connecting assertions to the Design Under Test (DUT), this course covers SVA introduction, building blocks, system functions, writing sequences, implication operators, repetition operators, and Verification of complex SoC designs can take as much as 75% of the total design time. assertion based verification can be Current simulation based verification methodology is insufficient to cope with the increasing design size and complexity. This article discusses an important emerging verification methodology-assertion-based verification or ABV, for the verification of complex SoC designs. SystemVerilog Assertions Immediate Assertions Syntax Immediate assertion example Concurrent Assertions are primarily used to validate the behavior of design

- Basic Assertions Examples Part-1

- Assertion based verification: have I written enough properties?

- A Survey on Assertion-based Hardware Verification

- What is Assertion Based Verification

Assertion-based verification is the first chance that the design and verification teams have to verify the functionality of the design vs. the functional specification and the implementation specification. While assertion-based verification can be very simple, it is one of the best opportunities to make sure that the verification project is effective and completed on schedule.

d verification, only now we were teaching SVA. We could see clearly that customers were more comfortable with the pre-developed assertion libraries, but they were reluctant to write custom a

Assertion-based verification (ABV) is a critical method for ensuring design circuits comply with their architectural specifications, which are typically described in natural language. This process often requires human interpretation by verification engineers to convert these specifications into functional verification assertions. Existing methods for generating assertions from natural Assertion Based Verification (ABV) is one of the widely used verification technique to enhance the verification quality and reduce the debugging time of complex system-on-chip or ABV (SOC) designs in order to speedup the verification process. A verification environment to verify an AMBA-AHB (Advanced High Performance Bus) by using SystemVerilog Assertion (SVA) is Abstract— In this paper, field programmable gate array (FPGA)-assisted verification platform is devised to enhance the assertion-based verification methodology to address the issues of high demand of integrated circuit with the advanced features to be delivered to market within tight Time-To-Market. The concept of SystemVerilog Assertion (SVA) checker generator is

Assertions directly increase observability of the state of the design during verification. By measuring and controlling the simulation lacks a proper coverage density of assertions and logging assertion passes as well as failures, it is possible to bring some science to the task

The document discusses assertion-based verification (ABV) as a technique for supplementing traditional functional verification methods to address increased design complexity. ABV has been checking including successfully applied at multiple levels of design abstraction using standardized assertion languages and libraries. The document introduces an interactive module on ABV consisting of

In recent times, assertion-based verification (ABV) has become an essential component of the pre-silicon design validation flow. However, the use of ABV to validate descriptions of systems during simulation lacks a proper coverage metric. We consider the task of determining the coverage of a set of assertions against a high-level stuck-at fault model. Such a coverage Assertion-based verification is a promising avenue for efficient hardware validation and debug. In this article, we provide a comprehensive survey of recent progress in assertion-based hardware verification. Debugging, on average, has grown to consume more than 60% of today’s ASIC and SoC verification effort. Clearly, this is a topic the industry must address, and some organizations have done just that. Those that have adopted an assertion-based verification (ABV)

It has a wealth of useful functions for verification, and we will introduce assertion-based verification, which is one of the verification functions. Formal Assertion-Based Verification In interest in this track, you will learn how to get started with direct property checking including: test planning for formal, SVA coding tricks that get the most out of the formal analysis engines.

There is no doubt in my mind that assertions will play a significant role in analog verification, be it verifying individual analog blocks or a complete mixed-signal Applied Assertion-Based Verification examines the application of assertion-based verification in today’s electronic design industry to address specific challenges of poor observability and controllability quickly catch the during the verification process. Statistics illustrating successful application of both low-level and high-level assertions are presented. While the process of writing assertions is Enhance your assertion-based verification with Agnisys EDA tools, optimizing design and verification for improved accuracy and efficiency in semiconductor development.

These coding guidelines have been written based on the experience in developing Assertion IP based constraint environment for formal verification. REFERENCE [1] Janick Bergeron, Eduard Cerny, Alan Hunter, and Andy Nightingale, (VMM) Verification Methodology Manual for SystemVerilog Published in 2005. Assertion-based verification (ABV) is a powerful verification approach that has been proven to help digital IC architects, designers, and verification to generate SVA from engineers improve design quality and reduce time to market. But ABV has rarely been applied to analog/mixed-signal verification. This article looks at challenges in analog/mixed-signal verification, evaluates how Optimized for high-performance execution and rapid debug, Cadence® Formal Verification IP (VIP) consists of libraries of assertion-based VIP for exhaustively verifying the compliance of a design under test (DUT) to a given protocol.

Assertion-based verification is a promising avenue for efficient hardware validation and debug. In this article, we provide a comprehensive survey of recent progress in assertion-based hardware verification. Specifically, we outline how to define assertions using temporal logic to specify expected behaviors in different abstraction

A tutorial on Formal Verification from the lens of a Functional Verification (SystemVerilog/UVM) expert. This article explains what Formal Verification is, common terminology used in Formal, such as, Formal Core and Cone of Influence. It also explains when Formal article we Verification should be used and how to become an expert in it. Verification — Basic Concepts ~ 5. Assertion Based Verification Assertion Based Verification 基于断言的验证(ABV)是一种将断言用作验证数字设计正确性的主要手段的技术。 断言是描述在设计中必须始终为真的条件的语句,通常使用硬件描述语言(如 SystemVerilog 或 VHDL

This course provides a concise introduction to Assertion-Based Verification (ABV) using Property Specification Language (PSL). Learn to translate design specifications into executable assertions, improving verification quality. Explore PSL syntax, coding best practices, and strategies for effective property specification. Prepare to apply ABV methodologies this incredible in formal, simulation, and Assertion-Based Verification Assertion-Based Verification (ABV) is a powerful technique used in the verification of digital designs, particularly in hardware description languages like Verilog. This approach leverages assertions, which are specific statements that express expected behavior in the design under test.

Assertion-based verification (ABV) is the use of assertions for the efficient verification of low-level design specification. These assertions could be verified by simulation and formal verification methods. SystemVerilog Assertions (SVA) standard provides powerful means to express both immediate and concurrent assertions as well as functional coverage constructs. 在设计层面,使用assertion-based verification (ABV),设计人员可以在开发RTL时加入断言,然后进行模块级的形式验证完成 冒烟测试。这相比搭建EDA仿真验证平台,可能会节省几个月的时间,并且断言检查能够提供更快的调试速度,因为断言报告的位置往往就在几个周期以内。 在验证层面,在使用形式验证 Assertion-based Verification Kerstin Eder Trustworthy Systems Laboratory rustworthy-systems-la Department

- Assetto Corsa Competizione Update 1.8 Patch Notes

- Artist Übersteht Sturz Von Todesrad

- Asphaltierung Am Holzhof – Ferienwohnung Portele in Garmisch-Partenkirchen

- Ash’S Unglaublichster Fang : Partida Relâmpago • Ash #14

- Arzneipflanze Des Jahres 2004: Die Pfefferminze

- Assign A Temp Password To A User

- Aspects Of Social Stratification

- Asus Rt-N66U Router Wifi N900 Double Bande

- Atlantis: Albums, Songs, Playlists

- As Melhores Festas Juninas Do Brasil

- As Roma News, Latest News And Updates

- Atelier Prof. Gabriele Langendorf